And then the scan flip-flops are configured to capture the response from the logic.In test mode, the scan flip-flops are first configured to perform shift operation so we can shift-in our test pattern.This mode is exactly similar to the original mode, and the Scan flip-flops can be simply ignored in this case in lieu of normal flip-flops.The flip-flops capture the data from pseudo-primary outputs of the combinational logic.The Normal Mode is activated when Scan Enable is logic-o.They capture the response from the logic and then apply the response to the logic in the next clock cycle.In normal mode, Scan Flip-Flops are configured to perform capture operation.Stitch FF/latch into a chain Modes of operation in Scan ChainĪs previously discussed, Scan Chain operates in two modes.In the VLSI industry, it is also known as DFT Insertion or DFT synthesis. This above process is known as Scan chain Insertion.

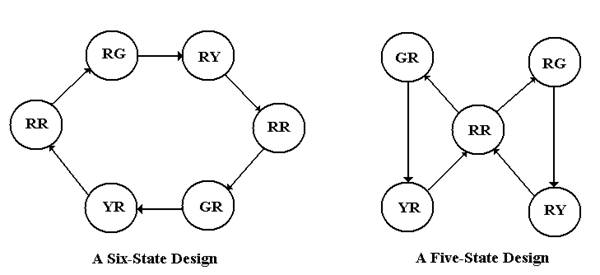

Scan remains one of the most popular structured techniques for digital circuits. The idea of the Internal Scan is to connect internal Flip-Flops and latches so that we can observe them in test mode. Hence the circuit now has two operation modes: Normal mode and Test mode. Now, we have the choice to either connect the combinational circuit output to the flip flop inputs (Normal Mode) or to connect it to Scan In pin (Test Mode).

But, in the newer design, we have disconnected the line using a multiplexer. In the previous circuit, the outputs of the combinational circuit were directly connected to the flip-flop inputs. In the modified design, the scan flip-flops are stitched together one after another in a Scan Chain. Let’s incorporate this new flip-flop into our design.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed